Simulation of pixel-size impact for optical brightfield wafer defect inspection

Introduction

These days, we do not get by a day without technology. Yet, we hardly stop to think about the very foundations that allow our way of life: semiconductors. Notably so, as the early computers took up a huge room. Today, we hold them in our palms, and fork out hundreds or thousands of dollars to buy them. With the world revolving around digital transformation and technology, the pressure is on semiconductor manufacturers to take on ever increasing challenges of creating higher complexity chip designs, explore new processes and materials. They also have to grapple with yield loss, which is an ever-present problem.

Typically, advanced semiconductor nodes are made by combining many processes together on a silicon wafer to fabricate the dies containing the intended designs. The dies are then diced into individual chips before being packaged and shipped. As complexity grows, so does the number of processes, and thus the manufacturing steps. These are all inception points for defects, which can cause the chips to fail and discarded. The earlier the defects can be caught, the less material wastage. Since fabs achieve economies of scale by high volume manufacturing [3], every discarded chip eats into operating margin. If the yield of a fab is low, these costs get passed onto the device manufacturer, and ultimately onto us, the consumers! Therefore, it is clear that yield control and improvement is critical and can be achieved by inspecting the dies before they proceed with wafer packaging.

Background

Wafer defects can be broadly classified in the following categories: (a) Particles, which are commonly dust or contamination in the air which gets stuck on the wafer surface and are small; (b) Scratches, typically caused by instrument faults and are continuous features; (c) Ripples, commonly due to film interference from coating defects during lithography and are irregularly shaped with fringing patterns; (d) Stains, due to contamination from lithography and are large patchy features. Depending on where the type of defects, they may be further classified into killer defects, also known as defects of interest. For example, a break in a data-carrying connector would not be acceptable.

Defect analysis involves finding the defect, and optical methods are well-suited for direct detection of defects. A few common optical detection methods are shown, rotating non-patterned wafer and specular reflection are commonly used for bare wafers, as suggested by their name. Dark field imaging is best suited for finding small defects such as particles and surface defects like faint scratches. Bright field imaging is used for macroscopic detection, and the results are most intuitive because the defect sensitivity is equivalent to the system resolution [4].

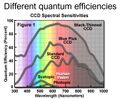

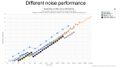

Automated defect detection of a substrate consists of a system that has both hardware and software components. The software component is for machine control, and detection algorithm which is detailed in the Methods. Focusing on the hardware imaging path, we have the imaging optics and camera. The imaging optics introduces an optical blur. The camera is our hardware of interest because it has a finite lifetime and usually undergoes multiple revisions in a product's lifecycle. However, choosing a camera suited for a particular application is complex as the camera itself has multiple parameters, such as pixel size, quantum efficiencies, and noise performance.

Methods

Results

Conclusions

Appendix

Camera parameters, taken from Photonic Science. [[7 actual CMOS camera.JPG|Camera parameters used for the simulation|https://photonicscience.com/products/optical-cameras/cooled-scmos-camera/]